University of Minnesota

### **Short Channel MOS Transistor**

Professor Chris H. Kim

University of Minnesota Dept. of ECE

chriskim@umn.edu www.umn.edu/~chriskim/

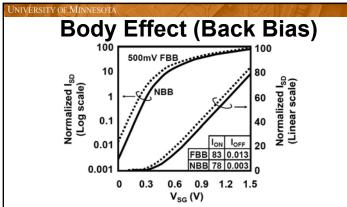

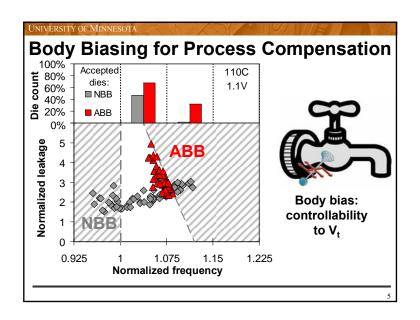

# Body Effect (Back Bias)

$$\begin{aligned} &V_{t0} = V_{fb} + \left|2\psi_{B}\right| + \frac{\sqrt{2qN_{a}\varepsilon_{si}}\left|2\psi_{B}\right|}{C_{ox}} \\ &V_{t} = V_{fb} + \left|2\psi_{B} + V_{sb}\right| + \frac{\sqrt{2qN_{a}\varepsilon_{si}}\left|2\psi_{B} + V_{sb}\right|}{C_{ox}} - V_{sb} \end{aligned} \qquad \begin{aligned} &\text{Gate} \qquad & \text{Body} \\ &V_{t} = V_{fb} + \left|2\psi_{B}\right| + \frac{\sqrt{2qN_{a}\varepsilon_{si}}\left|2\psi_{B} + V_{sb}\right|}{C_{ox}} &V_{sb} > 0 : \text{RBB} \\ &V_{t} = V_{fb} + \left|2\psi_{B}\right| + \frac{\sqrt{2qN_{a}\varepsilon_{si}}\left|2\psi_{B} + V_{sb}\right|}{C_{ox}} &V_{t} = V_{t} = V_{t} = V_{t} \end{aligned}$$

- Body effect degrades transistor stack performance

- However, we need a reasonable body effect for post silicon tuning techniques

- Reverse body biasing, forward body biasing

UNIVERSITY OF MINNESOTA

# Remember the Standard V<sub>t</sub> Equation?

$$V_{t} = V_{fb} + \left| 2\psi_{B} \right| + \frac{\sqrt{2qN_{a}\varepsilon_{si}|2\psi_{B}|}}{C_{ox}}$$

- **Y.** Taur, T. Ning, Fundamentals of Modern VLSI Devices, Cambridge University Press, 2002.

- Detailed derivation given in Taur's book

- · Basically, three terms

- Flat band voltage

- $-2\psi_B$ : the magic number for on-set of inversion

- Oxide voltage

2

- V<sub>t</sub> can be adjusted by applying FBB or RBB

- Essential for low power and high performance

- Will talk about body biasing extensively later on

4

UNIVERSITY OF MINNESOTA

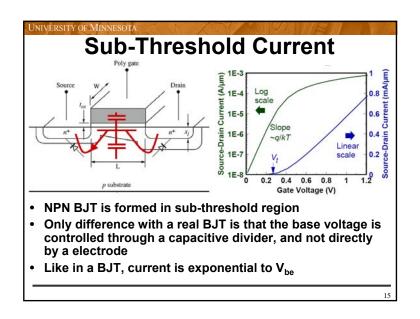

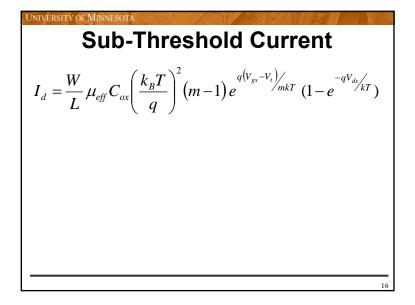

# **Sub-Threshold Swing**

$$S = m \frac{kT}{q} \ln 10 \ (mV/dec) \quad , \quad m = 1 + \frac{C_{dep}}{C_{ox}}$$

- Smaller S-swing is better

- Ideal case: m=1 (C<sub>ox</sub>>>C<sub>sub</sub>)

- Fundamental limit = 1 \* 26mV \* In10

= 60 mV/dec @ RT

- Can only be achieve by device geometry (FD-SOI)

- Typical case: m≈1.3

- S = 1.3 \* 26mV \* In10 ≈ 80 mV/dec @ RT

- At worst case temperature (T=110C), S ≈ 100 mV/dec

17

### University of Minnesota

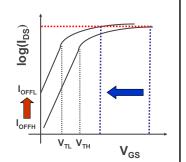

## V<sub>dd</sub> and V<sub>t</sub> Scaling

Performance vs Leakage:

$V_T \downarrow I_{OFF} \uparrow I_D(SAT) \uparrow$

$$I_{OFF} \propto rac{W_{eff}}{L_{eff}} K_1 e^{-V_T / mkT/q}$$

$$I_D(SAT) \propto \frac{W_{eff}}{L_{eff}} K_2 (V_{GS} - V_T)^2$$

$$I_D(SAT) \propto K_3 W_{eff} C_{ox} \upsilon_{SAT} (V_{GS} - V_T)$$

- ⇒ As V<sub>t</sub> decreases, sub-threshold leakage increases

- ⇒ Leakage is a barrier to voltage scaling

18

University of Minnesota

### V<sub>dd</sub> and V<sub>t</sub> Scaling

- V<sub>t</sub> cannot be scaled indefinitely due to increasing leakage power (constant sub-threshold swing)

- Example

CMOS device with S=100mV/dec has  $I_{ds}$ =10 $\mu$ A/ $\mu$ m @  $V_{\rm t}$ =500mV

$I_{\text{off}}$ =10 $\mu$ A/ $\mu$ m x 10<sup>-5</sup> = 0.1 nA/ $\mu$ m

Now, consider we scale the  $V_t$  to 100mV  $I_{off}$ =10 $\mu$ A/ $\mu$ m x 10<sup>-1</sup> = 1  $\mu$ A/ $\mu$ m

Suppose we have 1B transistors of width 1 $\mu$ m I<sub>sub</sub>=1 $\mu$ A/ $\mu$ m x 1B x 1 $\mu$ m = 100 A !!

19

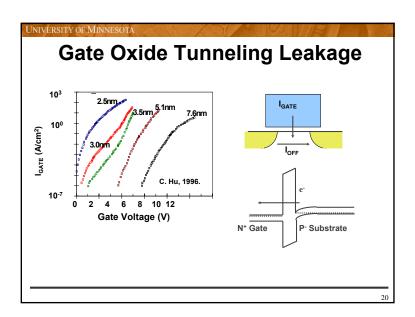

### UNIVERSITY OF MINNESOTA

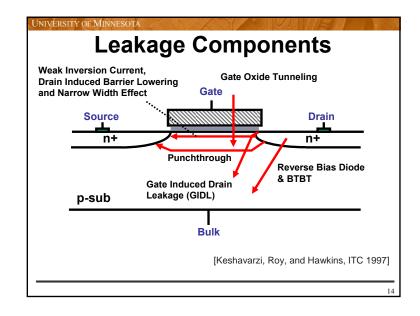

### **Gate Oxide Tunneling Leakage**

- Quantum mechanics tells us that there is a finite probability for electrons to tunnel through oxide

- Probability of tunneling is higher for very thin oxides

- NMOS gate leakage is much larger than PMOS

- Gate leakage has the potential to become one of the main showstoppers in device scaling

$$I_{gate} = AE_{ox}^{2}e^{-B/E_{ox}}$$

,  $E_{ox} = \frac{V_{dd} - V_{t}}{t_{ox}}$

21

# Band-to-Band Tunneling Leakage E<sub>C</sub> E<sub>V</sub> p(+)-side S/D junction BTBT Leakage • Reversed biased diode band-to-band tunneling - High junction doping: "Halo" profiles - Large electric field and small depletion width at the junctions

### UNIVERSITY OF MINNESOTA

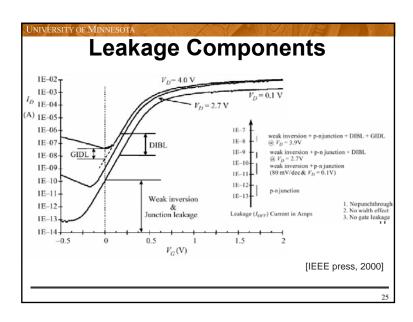

### **Gate Induced Drain Leakage (GIDL)**

- Appears in high E-field region under gate/drain overlap causing deep depletion

- Occurs at low  $V_q$  and high  $V_d$  bias

- Generates carriers into substrate from surface traps, band-to-band tunneling

- Localized along channel width between gate and drain

- Thinner oxide, higher V<sub>dd</sub>, lightly-doped drain enhance GIDL

- High field between gate and drain increases injection of carriers into substrate

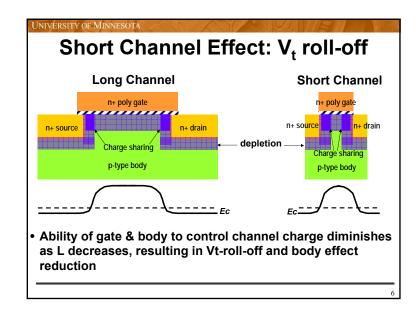

University of Minnesota **Narrow Width Effect** Gate V<sub>t</sub> width W Extra depletion Depletion region extends Channel region outside of gate controlled Side view of MOS transistor region Opposite to V₁ roll-off • Depends on isolation technology

23