## EE5323 Homework #2 The Devices and CMOS Inverter Due on 10/13 in class (or upload to WebCT)

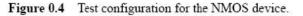

**1.** [chap. 3] An NMOS device is plugged into the test configuration shown below in Figure 0.4. The input  $V_{in} = 2V$ . The current source draws a constant current of 50 µA. R is a variable resistor that can assume values between  $10k\Omega$  and  $30 k\Omega$ . Transistor M1 experiences short channel effects and has following transistor parameters:  $k' = 120*10^{-6} V/A^2$ ,  $V_T = 0.3$ , and  $V_{DSAT} = 0.6V$ . The transistor has a W/L =  $2.5\mu/0.25\mu$ . For simplicity body effect and channel length modulation can be neglected. i.e  $\lambda=0$ ,  $\gamma=0$ .

$$V_{DD} = 2.5V$$

$R$

$V_{D}$

$W/L = 2.5\mu/0.25\mu$

$V_{S}$

$I = 50\mu A$

**a.** When  $R = 10k\Omega$  find the operation region,  $V_D$  and  $V_S$ .

**b.** When  $R = 30k\Omega$  again determine the operation region  $V_D$ ,  $V_S$ .

**c.** For the case of  $R = 10k\Omega$ , would V<sub>s</sub> increase or decrease if  $\lambda \neq 0$ . Explain qualitatively.

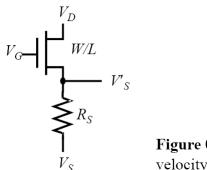

**2.** [chap. 3] Another equation, which models the velocity-saturated drain current of an MOS transistor is given by

$$I_{dsat} = \frac{1}{1 + (V_{GS} - V_t) / (E_{sat}L)} \left(\frac{\mu_0 C_{ox}}{2}\right) \frac{W}{L} (V_{GS} - V_T)^2$$

Using this equation it is possible to see that velocity saturation can be modeled by a MOS device with a source-degeneration resistor (see Figure 0.11).

**a.** Find the value of  $R_S$  such that  $I_{DSAT}(V_{GS}, V_{DS})$  for the composite transistor in the figure matches the above velocity-saturated drain current equation. Hint: the voltage drop across  $R_S$  is typically small. Channel length modulation can be ignored.

**b.** Given  $E_{sat} = 1.5 \text{ V/}\mu\text{m}$  and k' =  $\mu_0 C_{ox} = 20 \mu\text{A/V2}$ , what value of  $R_s$  is required to model velocity saturation. How does this value depend on W and L?

IMPORTANT INFORMATION: Permission is granted to copy and distribute this material for educational purposes only, provided that the complete bibliographic citation and following credit line is included: "Copyright 2002 J. Rabaey et al." This material may not be copied or distributed for commercial purposes without express written permission of the copyright holders.

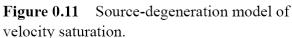

**3.** [chap. 5] Consider the following NMOS inverter. Assume that the bulk terminals of all NMOS device are connected to GND. Assume that the input IN has a 0V to 2.5V swing and there is no leakage current.  $V_{T0}=0.43$ ,  $\Phi_F=0.3$ .

**a.** Set up the equation(s) to compute the voltage on node *x*. Assume the body effect coefficient  $\gamma=0.5 \left[\sqrt{\mathbf{v}}\right]$ .

**b.** What are the modes of operation of device M2? Assume  $\gamma=0$ .

**c.** What is the value on the output node OUT for the case when IN =0V? Assume  $\gamma$ =0.

**d.** Assuming devices are in velocity saturation region,  $V_{DSAT} = 0.63V$  and  $\gamma=0$ , derive an expression for the switching threshold (VM) of the inverter. Recall that the switching threshold is the point where VIN= VOUT. Assume that the device sizes for M1, M2 and M3 are (W/L)<sub>1</sub>, (W/L)<sub>2</sub>, and (W/L)<sub>3</sub> respectively. What are the limits on the switching threshold?

For this, consider two cases:

i) (W/L)<sub>1</sub> >> (W/L)<sub>2</sub>

ii) (W/L)<sub>2</sub> >> (W/L)<sub>1</sub>

IMPORTANT INFORMATION: Permission is granted to copy and distribute this material for educational purposes only, provided that the complete bibliographic citation and following credit line is included: "Copyright 2002 J. Rabaey et al." This material may not be copied or distributed for commercial purposes without express written permission of the copyright holders.

4. [chap. 5] Sizing a chain of inverters.

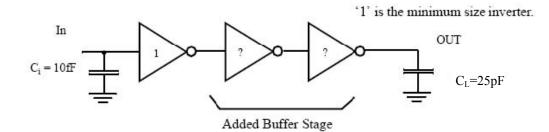

**a.** In order to drive a large capacitance ( $C_L = 25 \text{ pF}$ ) from a minimum size gate (with input capacitance  $C_i = 10 \text{fF}$ ), you decide to introduce a two-staged buffer as shown in Figure 5.12. Assume that the propagation delay of a minimum size inverter is 70 ps. Also assume that the input capacitance of a gate is proportional to its size. Determine the sizing of the two additional buffer stages that will minimize the propagation delay. Assume the junction capacitance to gate capacitance ratio  $\gamma=1$ .

**b.** If you could add any number of stages to achieve the minimum delay, how many stages would you insert? What is the propagation delay in this case?

c. Describe the advantages and disadvantages of the methods shown in (a) and (b).

**d.** Determine a closed form expression for the power consumption in the circuit. Consider both the gate and junction capacitances in your analysis. What is the power consumption for a supply voltage of 2.5V, an activity factor of 1, and a clock period of *T*?

Figure 5.12 Buffer insertion for driving large loads.

IMPORTANT INFORMATION: Permission is granted to copy and distribute this material for educational purposes only, provided that the complete bibliographic citation and following credit line is included: "Copyright 2002 J. Rabaey et al." This material may not be copied or distributed for commercial purposes without express written permission of the copyright holders.