# **Efficient Crosstalk Estimation**\*

Martin Kuhlmann, Sachin S. Sapatnekar, Keshab K. Parhi Department of Electrical and Computer Engineering University of Minnesota, Minneapolis MN 55455, USA Email: {kuhlmann, sachin, parhi}@ece.umn.edu

#### Abstract

With the reducing distances between wires in deep submicron technologies, coupling capacitances are becoming significant as their magnitude becomes comparable to the area capacitance and fringing capacitance of a wire. This causes an increasing susceptibility to failure due to inadvertent noise, and leads to a requirement for accurate noise estimation. An incorrect estimation of the noise could lead either to circuit malfunction in case of under-estimation, or to wasted design resources due to overestimation. This paper presents a new time-efficient method for the precise estimation of crosstalk noise. While existing fast noise estimation metrics may overestimate the coupling noise by several orders of magnitude, the proposed metric computes the coupling noise with a good accuracy as compared to SPICE.

## 1 Introduction

In the past, timing and power analysis have been the critical criteria to be optimized in the design process. With the use of deep sub-micron technologies, shrinking geometries have led to a reduction the self-capacitance of wires while increasing coupling capacitances as wires are brought closer together. In conjunction with increases in operating frequencies, noise analysis and avoidance is becoming as critical a factor in circuit design as timing or power. For present day processes, the coupling capacitance can be as high as the sum of the area capacitance and the fringing capacitance of a wire, and trends indicate that the role coupling capacitances will be even more dominant in the future as feature sizes shrink [1, 2].

One of the important effects of coupling capacitances is that they may induce unwanted voltage spikes in neighboring nets. A net on which a switching event occurs is termed an *aggressor* and the net on which it produces a noise spike is referred to as a *victim*. Typically, an aggressor net is physically adjacent to a victim net and they may be modeled as being connected by a distributed coupling capacitance. Hence, a switching event in the aggressor net while the victim net is silent can result in the injection of a  $C \frac{dv}{dt}$  current into the victim net, causing an electrical spike. In time, as the aggressor net completes its transition, this electrical spike dies down to zero. However, a large coupling capacitance relative to the self-capacitance of the wire can cause a large inadvertent spike on the victim that may cause a spurious switching event, potentially leading to an unintended state being latched and thereby changing the functionality of the circuit.

Various transient analysis techniques can be used to estimate noise. Circuit or timing simulation techniques, such as SPICE [3], may be used, but these are computationally expensive and are not conducive to use on large systems, particularly when fast noise evaluations for noise optimization purposes are required. When the system is modeled as a linear circuit, linear model order reductions such as [4, 5, 6] may be used, and these have been incorporated in a noise evaluation system [7, 8]. These model order reduction techniques help in reducing the computational cost, but in several cases, the cost is still unacceptably high for an optimization system that would use a noise metric to select the circuit parameters for noise-free behavior. Using modern moment matching methods, it may still require more than a day to compute the noise in a modern microprocessor [9]. An example of such a situation is in designing a physical design system where optimizations such as buffer insertion [10], spacing [11] or routing criteria are to be introduced [12, 13, 14]; such systems must, of necessity, use much simpler noise metrics. Most existing physical design systems for noise optimization use extremely simple noise models such as one where the noise is computed as being proportional to the overlap between wires [12, 13, 14]. While this is not an unreasonable first-order model, it fails to capture deeper intricacies such as the effects of the slope of the aggressor transient waveform, the effects of the ratio of the

<sup>\*</sup>This work was supported in part by the Defense Advanced Research Projects Agency under contract number DA/DABT63-96-C-0050, by the Semiconductor Research Corporation under contract 98-DJ-609 and by the National Science Foundation under award CCR-9800992.

self-capacitance to the coupling capacitance, etc. As these simple formulae do not have a concrete electrical and circuit theoretic formulation, they are liable to be inaccurate.

A fast metric for coupled noise estimation based on model-order reduction techniques was recently presented in [9]. We will describe this metric in detail in Section 3, and it forms the foundation for this work. However, while it is an excellent first effort, its limitations lie in the fact that it computes only an upper bound on the circuit noise, a value that is overly pessimistic. While we will explicitly list and quantify its other weaknesses later in this paper, it suffices to observe here that its accuracy is limited to short wires and relatively slow slew rates of more than 100ps. In the near future, when clock frequencies of 1-2 GHz will be common, much faster slew rates are expected and due to resistive shielding slew rates of 20ps to 100ps can obtained at the driver output. Hence, the upper bound is too pessimistic and is liable to predict noise spikes that exceed the supply voltage, which is impossible in a pure RC circuit. This motivates the need for a more accurate metric for noise analysis to address these problems.

This paper presents an improved metric for a more precise estimation of crosstalk noise. Its computational complexity is comparable to the Devgan metric and its derivation is, indeed, inspired by the techniques used in that metric. Our experimental results show the improved accuracy of the method.

The paper is organized as follows. Section 2 presents the basics of crosstalk estimation, followed by a brief presentation of Devgan's metric in Section 3. Our new noise estimation method is described in Section 4 presents the new efficient noise estimation method, with procedures for efficient computation and an analysis of the computational complexity being provided in Section 5. Experimental results are listed and Section 6 and a set of concluding remarks round up the paper in Section 7.

#### 2 Basics of crosstalk estimation

The work in [9] introduced a method for computing an estimate of the coupling noise between wires using the final value theorem [15]. The method was elegant in its simplicity in that it permitted the noise estimate to be calculated in a similar manner to the Elmore delay [16]. This led to its adoption for use in physical design in [10, 11], using an extension of Elmore delay optimization methods for this purpose.

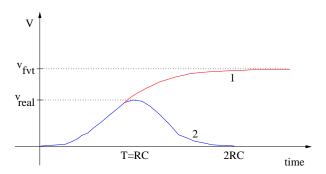

The method proposed in this work begins with the same equations as [9], but performs a different analysis for noise estimation. While Devgan's metric is guaranteed to be an upper bound on the noise, we will show that it may be too pessimistic, and that it may be wiser not to employ the final value theorem to develop a metric based on this approach for systems with fast switching transitions at gate outputs. To illustrate this, we show the difference between the two methods in Figure 1. In [9], the aggressor net is assumed to be excited by a forcing function that is similar to a step function, but with a nonzero transition time and a finite slope. This slope leads to a noise spike in the victim net of the type shown by graph 2 in the figure. However, to ease the computation, it was assumed in [9] that the increasing ramp is infinite, leading to the response shown by graph 1 in the figure. This is easily proven to be an upper bound on the noise shown in graph 2.

Figure 1. Different model for analyzing the noise. 1 shows final value theorem method, 2 shows real noise signal used for the proposed method

However, this upper bound is not necessarily tight, and we will show instances in our experimental results where the bound leads to meaningless results since the obtained value is larger than  $V_{dd}$ . As shown in Figure 2, the noise reaches its maximum value at some time after the aggressor net switches, after which it again decreases towards zero. Nevertheless, it is certainly true that in order to approximate the noise, the slew rate of the aggressor plays an important role since it influences the  $C \frac{dv}{dt}$  current injected into the victim through the coupling capacitance. This current causes the voltage to drop along the wire resistance of the victim net. Assuming the victim net to be at zero potential initially, the voltage at a node on the victim net first increases due to this injection. As the transient on the aggressor net settles, the magnitude of the injected current reduces, and the noise on the victim net dies down to zero.

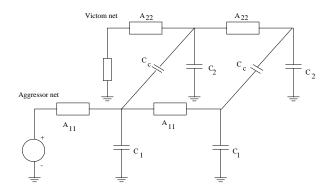

We will now soon reproduce the essentials of Devgan's approach to formulating the problem, and we will utilize the same basic notation to express our solution to the problem. The basic set of equations for a circuit of the type shown in Figure 2, with net 1 being the aggressor and net 2 being the victim net, initially at ground potential, can be written as follows:

$$\begin{bmatrix} C_1 & C_c^T \\ C_c & C_2 \end{bmatrix} \begin{bmatrix} \dot{v}_1 \\ \dot{v}_2 \end{bmatrix} = \begin{bmatrix} A_{11} & 0 \\ 0 & A_{22} \end{bmatrix} \begin{bmatrix} v_1 \\ v_2 \end{bmatrix} + \begin{bmatrix} B_1 \\ 0 \end{bmatrix} v_s, \quad (1)$$

Figure 2. Circuit schematic with aggressor and victim net for coupled noise

where  $v_1$  is a vector of node voltages in the aggressor net,  $v_2$  is a vector of node voltages in the victim net, and  $v_s$ is the input to the aggressor net. In (1), the zeros in the conductance matrix indicate the fact that there is no resistive path between net 1 and net 2. The zero on the right hand side is due to the fact that the excitation is applied only to net 1 and net 2 is connected to ground. This matrix system can be rewritten in the Laplace domain as

$$sC_1V_1 + sC_c^TV_2 = A_{11}V_1 + B_1V_s,$$

$$sC_cV_1 + sC_2V_2 = A_{22}V_2$$

(2)

## **3** Description of Devgan's Metric

Using Equation (2), Devgan computes the transfer function

$$H(s) = \frac{V_2(s)}{V_s(s)}$$

=  $-\left[(sC_2 - A_{22}) + sC_c (sC_1 - A_{11})^{-1} sC_c^T\right]^{-1} \cdot sC_c (sC_1 - A_{11})^{-1} B_1$  (3)

Applying an input voltage,  $V_s$ , to the aggressor net in the form of a finite ramp leads to a solution to the circuit. However, since this could lead to a messy solution procedure, Devgan applies an input of the form  $k/s^2$ . This corresponds to an infinite ramp of slope k, the response to which, as observed earlier, is a monotone increasing waveform on the victim whose final value provides an upper bound on the noise. Applying the final value theorem leads to the result

$$V_{2,max} = -A_{22}^{-1}C_c A_{11}^{-1}B_1 k \tag{4}$$

To simplify the process of calculating this, a circuit interpretation was provided. Equation (4) can be rewritten as

$$V_{2,max} = -A_{22}^{-1}C_c \dot{V}_{1,ss},\tag{5}$$

where

$$\dot{V}_{1,ss} = -A_{11}^{-1}B_1k. \tag{6}$$

The circuit interpretation of this implies that (6) may be solved by applying an excitation of  $B_1k$  to the aggressor net 1 while open-circuiting all capacitances connected to it. This implies that for an RC aggressor line with no path to ground, the value of  $\dot{V}_{1,ss} = k$  at all nodes. Considering the circuit interpretation of  $C_c \dot{V}_{1,ss}$  in Equation (5), each coupling capacitance can be replaced by a current source of value k times the coupling capacitance at the node; any capacitances to ground are removed. Let us represent this vector of current sources be  $I_c$ . Then solving (5) amounts to solving

$$V_{2,max} = -A_{22}^{-1}I_c.$$

(7)

Thus, the value of  $V_{2,max}$  can be obtained by solving net 2 with the above transformation on all capacitances. This may be carried out by means of a tree traversal.

#### 3.1 Limitations of this Metric

The metric described above has several limitations:

- The noise voltage in the victim net is proportional to the slope of the transient of the input voltage ramp. In case of fast slew rates, the noise of the victim increases in an unbounded manner. In the extreme situation where the input is a step function, the noise in the victim net goes to ∞. This is clearly impossible since the supply voltage limits the maximum noise that can be induced.

- The magnitude of the induced noise has no dependence whatsoever on the capacitances to ground of either the aggressor or the victim. This is clearly incorrect, since a coupling capacitance that is negligible in comparison with the capacitance to ground would lead to a negligible crosstalk value. Moreover, there is no dependence on the resistances in the aggressor net, implying that the length of the aggressor net is irrelevant to the value of the noise spike.

In Tables 1 and 2, we support the two arguments above by explicit verification. The results in the two tables show the noise spike in Volts using parameters for a  $0.25\mu$ m technology and for a  $0.18\mu$ m technology, respectively. For the length of the victim net, four different lengths, varying from 0.5mm to 5mm, have been assumed. Additionally, four different slew rates have been used. The "x" in the Tables 1 and 2 represents the independence of the noise to the length of the aggressor net. It is seen from the tables that the predicted noise spike greatly exceeds the  $V_{dd}$  value. According to our HSPICE simulations (listed in Section 6), the magnitude of the crosstalk spike on a victim net of constant length can vary by as much as 64 % with variations in the length of the aggressor.

Table 1. Noise simulation results in Volt of Devgan's metric using a 0.25  $\mu m$  CMOS technology and V\_{dd}=2.15V

| wires   | 20ps   | 50ps   | 100ps  | 250ps  |

|---------|--------|--------|--------|--------|

| x-5mm   | 55.82V | 22.17V | 16.75V | 6.66V  |

| x-2.5mm | 14.23V | 5.65V  | 4.27V  | 1.7V   |

| x-1mm   | 2.408V | 0.956V | 0.723V | 0.287V |

| x-0.5mm | 0.657V | 0.261V | 0.197V | 0.078V |

Table 2. Noise simulation results in  ${\bf V}$  of Devgan's metric using a 0.18  $\mu$  m CMOS technology, V\_{dd}=1.65V

| wires   | 20ps   | 50ps   | 100ps  | 250ps  |

|---------|--------|--------|--------|--------|

| x-5mm   | 45.25V | 17.97V | 13.58V | 5.4V   |

| x-2.5mm | 11.54V | 4.58V  | 3.462V | 1.38V  |

| x-1mm   | 1.95V  | 0.775V | 0.586V | 0.233V |

| x-0.5mm | 0.532V | 0.211V | 0.160V | 0.064V |

# 4 A new metric for precise crosstalk estimation

We will persist with the notation introduced above, as far as possible, and model the response of the input voltage to a ramp. The motivation for studying the response to a ramp is that eventually, we will express a step-like transient with a linear rise transient and a slope of k as a summation of three ramps.

For a ramp input, we may expand  $V_1(s)$  using the series:

$$V_1(s) = v_{10}s^{-2} + v_{11}s^{-1} + v_{12} + v_{13}s^1 + \dots$$

(8)

Similarly, the voltage  $V_2(s)$  can be represented as

$$V_2(s) = v_{20}s^{-1} + v_{21} + v_{22}s^1 + v_{23}s^2 + \dots$$

(9)

These specific forms for the series have been chosen to be consistent with the final value theorem. If an infinite ramp is applied to the aggressor, the response  $v_1(t)$  on the aggressor net will go towards infinity as  $t \to \infty$ . This is captured by ensuring a nonzero value for  $v_{10}$ . Similarly, for the latter equation,  $v_2(t)$  approaches  $v_{20}$  as its final value, consistent with the observation that the response on the victim net saturates to a constant on the application of an infinite ramp. The motivation for capturing the response to the infinite ramp will become apparent later, but a synopsis of the explanation is that the input waveform to the aggressor is represented by a sum of ramps. Using the series expansions for the voltages  $V_1$  and  $V_2$  and substituting them in Equation (3) leads to:

$$(sC_1 - A_{11})(v_{10}s^{-2} + v_{11}s^{-1} + v_{12} + v_{13}s^{1} + \dots) + sC_c^T(v_{20}s^{-1} + v_{21} + v_{22}s^{1} + v_{23}s^{2} + \dots) = B_1ks^{-2}, (10)$$

$$(sC_2 - A_{22})(v_{20}s^{-1} + v_{21} + v_{22}s^1 + v_{23}s^2 + \dots) + sC_c(v_{10}s^{-2} + v_{11}s^{-1} + v_{12} + v_{13}s^1 + \dots) = 0.$$

(11)

As in AWE [4], we may conclude that these equations are satisfied if the coefficients of all  $s^i$  on the left hand side are the same as those on the right hand side. Hence, we obtain from (10):

$$s^{-2}: \qquad A_{11}v_{10} = -B_1k,$$

$$s^{-1}: \qquad A_{11}v_{11} - C_1v_{10} = 0,$$

$$s^{0}: \qquad A_{11}v_{12} - C_1v_{11} = C_c^T v_{20},$$

$$s^{i\geq 1}: \qquad A_{11}v_{1i} - C_1v_{1(i-1)} = C_c^T v_{2(i-2)}.$$

(12)

Solving this for  $v_{1i}$  leads to

$$s^{-2}: v_{10} = -A_{11}^{-1}B_1k,$$

$$s^{-1}: v_{11} = A_{11}^{-1}C_1v_{10},$$

$$s^{0}: v_{12} = A_{11}^{-1}(C_1v_{11} + C_c^Tv_{20}),$$

$$s^{i\geq 1}: v_{1i} = A_{11}^{-1}(C_1v_{1(i-1)} + C_c^Tv_{2(i-2)}).$$

(13)

Similarly, from (11), the following results can be obtained for  $v_{2i}$ :

$$s^{-1}: v_{20} = A_{22}^{-1}C_{c}v_{10},$$

$$s^{0}: v_{21} = A_{22}^{-1}(C_{c}v_{11} + C_{2}v_{20}),$$

$$s^{i\geq 1}: v_{2i} = A_{22}^{-1}(C_{c}v_{1i} + C_{2}v_{2(i-1)}).$$

(14)

In order to obtain a closed form for the voltage  $v_2(t)$ , let us consider its response to an infinite rising ramp (see Figure 1, graph 1). For  $t \to \infty$ ,  $v_2(t)$  approaches a constant value  $c \neq 0$ . For  $t \to 0$ ,  $v_2(t)$  is 0. Using the initial and final value theorems, the following form of transfer function is appropriate:

$$V_2(s) = \frac{1}{s} \cdot \frac{a_0 + a_1 s + \dots + a_{n-1} s^{n-1}}{1 + b_1 s + \dots + b_{n-1} s^{n-1} + b_n s^n}.$$

(15)

The initial value theorem results in  $v_2(0) = 0$ , and the final value theorem results in  $v_2(t \to \infty) = a_0$ .

The order of approximation depends on the degree of the denominator polynomial. For computational efficiency, we will focus on the approximation of the following form:

$$V_2(s) = \frac{1}{s} \frac{a_0}{1+b_1 s} \tag{16}$$

which has the inverse Laplace transform

$$v_2(t) = a_0 \cdot (1 - e^{-\frac{t}{b_1}}). \tag{17}$$

Performing moment matching for the expressions for  $V_2(s)$ in the equations (11) and (16) leads to:

$$a_{0_j} = v_{20_j} \tag{18}$$

$$b_{1_j} = -\frac{v_{21_j}}{v_{20_j}} = -\frac{v_{21_j}}{a_{0_j}},$$

(19)

where j is the node number where the noise is computed.

### **5** Efficient Computation Techniques

#### 5.1 Circuit Interpretation and Computation

The equations for the maximum voltage and the time constant obtained in Section 2 can be physically explained. Recalling that

$$a_{0_j} = v_{20_j} = -\left(A_{22}^{-1}C_c A_{11}^{-1}B_1 k\right)_j \quad (20)$$

$$b_{1_j} = -\frac{v_{21_j}}{v_{20_j}} \tag{21}$$

$$= - \frac{\left(A_{22}^{-1} \left(C_c v_{11} + C_2 v_{20}\right)\right)_j}{a_{0_j}}, \qquad (22)$$

where j represents the  $j^{th}$  node in the design, and  $v_1$  and  $v_2$  are given by Equations (13) and (14), respectively. As in Devgan's work, we may ascribe a physical meaning to these equations. We first point out that  $a_0$  is identical to the noise value calculated by Devgan and can be calculated similarly. This is consistent with the fact that  $a_0$  represents the final value of the response waveform in the reduced order model in Equation (16). Similar principles may also be used to determine  $b_1$  efficiently. The procedure may be summarized as follows:

- The first step involves the calculation of  $v_{20}$  at every node in the victim net. Note that this has fortuitously already been carried out in the process of computing  $a_0$ .

- Next, it is necessary to calculate  $v_{11}$  by solving

$$v_{11} = A_{11}^{-1} C_1 v_{10} \tag{23}$$

The quantity  $v_{10}$  has already been seen to be a value of k at each node. Therefore finding  $v_{11}$  involves the solution of the aggressor net with all coupling capacitances removed, and all self-capacitances to ground,  $C_{1i}$ , replaced by a current source of value  $-C_{1i}k$ . The solution to the resulting circuit yields the vector  $v_{11}$ .

• Having computed  $v_{11}$  and  $v_{20}$ , the next step is to solve the equation

$$v_{temp} = A_{22}^{-1} \left( C_c v_{11} + C_2 v_{20} \right) \tag{24}$$

This physically corresponds to solving the victim net, modified so that each coupling capacitance,  $C_{ci}$ , is replaced by a current source of value  $-C_{cj}(v_{11})_j$ , and each self-capacitance to ground,  $C_{2j}$  is replaced by a current source  $-C_{2j}v_{20}$ ; the solution to the resulting circuit yields the vector  $v_{temp}$ .

• Finally,  $b_{1_j}$  is calculated by dividing the  $j^{th}$  element of  $v_{temp}$  by the  $j^{th}$  element of  $a_0$ .

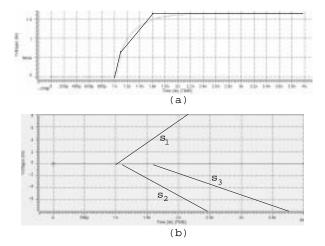

### 5.2 Input Modeling

The input signal, which is the output of the gate driving the wire, is similar to an exponential waveform. It is quite difficult to simulate such an input. Hence, a piece-wise linear interpolation is done (see Fig. 3 (a)). The corresponding model for the simulations is shown in Fig. 3 (b). For the sake of simplicity, three lines  $s_1, s_2$  and  $s_3$  with slope  $m_1, m_2$  and  $m_3$  have been chosen, respectively, where the slopes can be obtained by examining the piece-wise linear model from Fig. 3 (a).

Figure 3. (a) The input of the aggressor net and (b) the model for the simulations

#### 5.3 Computational Complexity

The computational complexity of the proposed metric can be obtained by examining the equations (20) to (24). The computation of  $a_0$  does not differ from the computation in [9]. Hence, four tree traversals and one multiplication of a diagonal matrix vector by a vector are required. The tree traversal and the multiplication are of the order O(n), where n is the number of segment points (see section 6). In order to obtain  $v_{11}$ , four tree traversals and a diagonal

|           | HSPICE |      |       |       | proposed metric |      |       |       | Devgan's metric |       |       |       |

|-----------|--------|------|-------|-------|-----------------|------|-------|-------|-----------------|-------|-------|-------|

| wires     | 20ps   | 50ps | 100ps | 250ps | 20ps            | 50ps | 100ps | 250ps | 20ps            | 50ps  | 100ps | 250ps |

| 5-5mm     | 390    | 340  | 300   | 237   | 590             | 567  | 463   | 447   | 55820           | 22170 | 16750 | 6660  |

| 5-2.5mm   | 229    | 187  | 154   | 103   | 251             | 206  | 167   | 144   | 14230           | 5650  | 4270  | 1700  |

| 5-1mm     | 130    | 91   | 67    | 38    | 129             | 104  | 79    | 68    | 2408            | 956   | 723   | 287   |

| 5-0.5mm   | 25     | 16   | 9     | 5     | 38              | 23   | 13    | 7     | 657             | 261   | 197   | 78    |

| 2.5-2.5mm | 308    | 248  | 210   | 187   | 540             | 417  | 295   | 216   | 14230           | 5650  | 427   | 1700  |

| 2.5-1mm   | 130    | 84   | 53    | 27    | 189             | 116  | 69    | 33    | 2408            | 956   | 723   | 287   |

| 2.5-0.5mm | 46     | 27   | 23    | 11    | 86              | 44   | 27    | 16    | 657             | 261   | 197   | 78    |

| 1-1mm     | 120    | 90   | 55    | 30    | 179             | 103  | 66    | 29    | 2408            | 956   | 723   | 287   |

| 1-0.5mm   | 47     | 27   | 14    | 7     | 68              | 34   | 17    | 7     | 657             | 261   | 197   | 78    |

Table 3. Noise simulation results in mV of HSPICE and of the proposed metric, using a 0.25  $\mu$ m CMOS technology and V\_{dd}=2.15V

matrix-vector multiplication are required. For the computation of the entire numerator an additional diagonal matrixvector multiplication and two tree traversals are necessary. Finally, a division of order O(n) has to be used to obtain the values of  $b_1$  at every point along the victim net. Hence, ten tree traversals, four diagonal matrix-vector multiplications and one division is required to compute the noise along the victim net. Compared with the metric of Devgan, this corresponds to an increase in the number of tree traversals and multiplication/division by 2.5x and 4x, respectively. However, by realizing that Devgan's scheme required less than half a second to compute the noise in a circuit with 500,000 elements, this increase in complexity is tolerable.

#### 6 **Results and Comparison**

In accordance with [2], SPICE-files have been obtained for four different wire lengths, varying from 5mm to 1mm for the aggressor net and from 5mm to 0.5mm for the victim net, respectively. The wire resistances and capacitances have been distributed every  $100\mu m$ . Hence, the number of segment points is equal to the length of the victim net divided by  $100\mu m$ . Victim nets of longer length than the aggressor net have not been considered due to the fact that these cases can be modeled by wires of equal length. The driver of the aggressor net is simulated as a voltage source with output slope  $k = V_{dd}/T$  and a driver resistance  $R_d$ . The input modelling at the driver output was described in section 5.2.

The results of the HSPICE simulations are presented in the Tables 3 and 4 for a 250nm and a 180nm CMOS technologies. Aggressors and victims of various length are chosen. The entry 2.5mm-1mm implies an aggressor net of length 2.5mm and a victim net that is 1mm long. The noise is always measured at the end of the victim net. The slew rates of 20ns, 50ns, 100ns and 250ns represent the voltage rise and fall time at the input. By examining Tables 3 and 4, it can be seen that the results of the new metric have a good accuracy compared to SPICE. The noise estimation is slightly over-estimated for victim nets with equal length to the aggressor net. The error in the noise prediction is caused by the first order model. However, using higher order models does not lead to better approximations because we found that the poles of the transfer function in (15) become complex. By comparing the results of the new metric with the results of Devgan (these results are repeated from Section 3.1), the improvement in noise estimation is obvious. While the noise is overestimated by up to two orders of magnitude using Devgan's metric, the proposed metric provides results that are close to the actual SPICE simulations.

# 7 Conclusion

This paper presented a new method for the coupled noise estimation. The proposed metric computes the noise according to the sink capacitances and conductances of the aggressor net and the victim net, respectively, the coupling capacitance between those two nets and the rise time of the aggressor signal. The noise waveform is computed using a closed form leading to a short computation time. While previously the coupling noise was over-estimated by up to two orders of magnitude, assuming slew rates of less than 100ps and long or medium length wires, the coupling noise can be computed within a good accuracy compared to SPICE. This results have been obtained by comparing the proposed metric results with SPICE simulation results.

# References

J. Cong, "Challenges and opportunities for design innovations in nanometer technologies," tech. rep., Semiconductor Research Corporation, 1998.

Table 4. Noise simulation results in mV of HSPICE and of the proposed metric, using a 0.18  $\mu$ m CMOS technology and V\_{dd}=1.65V

|           | HSPICE |      |       | proposed metric |      |      |       | Devgan's metric |       |       |       |       |

|-----------|--------|------|-------|-----------------|------|------|-------|-----------------|-------|-------|-------|-------|

| wires     | 20ps   | 50ps | 100ps | 250ps           | 20ps | 50ps | 100ps | 250ps           | 20ps  | 50ps  | 100ps | 250ps |

| 5-5mm     | 336    | 306  | 284   | 252             | 636  | 608  | 578   | 435             | 45250 | 17970 | 13580 | 5400  |

| 5-2.5mm   | 197    | 168  | 136   | 108             | 292  | 268  | 206   | 144             | 11540 | 4580  | 3462  | 1380  |

| 5-1mm     | 98     | 63   | 36    | 21              | 95   | 73   | 46    | 26              | 1950  | 775   | 586   | 233   |

| 5-0.5mm   | 35     | 18   | 10    | 5               | 39   | 26   | 15    | 8               | 532   | 211   | 160   | 64    |

| 2.5-2.5mm | 246    | 212  | 172   | 118             | 448  | 374  | 267   | 152             | 11540 | 4580  | 3462  | 1380  |

| 2.5-1mm   | 103    | 66   | 38    | 22              | 153  | 95   | 45    | 26              | 1950  | 775   | 586   | 233   |

| 2.5-0.5mm | 36     | 18   | 11    | 7               | 54   | 26   | 15    | 10              | 532   | 211   | 160   | 64    |

| 1-1mm     | 161    | 93   | 58    | 30              | 277  | 114  | 68    | 37              | 1950  | 775   | 586   | 233   |

| 1-0.5mm   | 55     | 27   | 15    | 7               | 87   | 35   | 23    | 13              | 532   | 211   | 160   | 64    |

- [2] Semiconductor Industry Association, "National Technology Roadmap for Semiconductors," 1997.

- [3] L. W. Nagel, "SPICE2, A Computer Program to Simulate Semiconductor Circuits," in *Technical Report ERL-M520*, (UC-Berkely), May 1975.

- [4] L. T. Pillage and R. A. Rohrer, "Asymptotic waveform evaluation for timing analysis," *IEEE Transactions on Computer-Aided Design*, vol. 9, pp. 352–366, Apr. 1990.

- [5] P. Feldmann and R. W. Freund, "Efficient linear circuit analysis by Padé approximation via the Lanczos process," *IEEE Transactions on Computer-Aided Design*, vol. 14, pp. 639–649, May 1995.

- [6] A. Odabasioglu, M. Celik, and L. T. Pileggi, "PRIMA: Passive reduced-order interconnect macromodeling algorithm," *IEEE Transactions on Computer-Aided Design*, vol. 17, pp. 645–654, Aug. 1998.

- [7] K. Shepard and V. Narayanan, "Noise in Submicron Digital Design," in *Proceedings of IEEE/ACM In*ternational Conference on Computer Aided Design, pp. 524–531, 1996.

- [8] K. Shepard, V. Narayanan, P. C. Elmendorf, and G. Zheng, "GlobalHarmony: Coupled noise analysis for full-chip RC interconnect networks," in *Proceed*ings of the IEEE/ACM International Conference on Computer-Aided Design, pp. 139–146, 1997.

- [9] A. Devgan, "Efficient coupled Noise Estimation for On-Chip Interconnects," in *Proceedings of the IEEE/ACM International Conference on Computer-Aided Design*, pp. 147–151, 1997.

- [10] C. J. Alpert, A. Devgan, and S. T. Quay, "Buffer insertion for noise and delay optimization," in *Proceedings of the ACM/IEEE Design Automation Conference*, pp. 362–367, 1998.

- [11] P. Morton and W. Dai, "An efficient sequential quadratic programming formulation of optimal wire spacing for crosstalk noise avoidance routing," in

ACM International Symposium on Physical Design, pp. 22–28, 1999.

- [12] T. Gao and C. L. Liu, "Minimum crosstalk switchbox routing," in *Proceedings of the IEEE/ACM International Conference on Computer-Aided Design*, pp. 610–615, 1994.

- [13] T. Xue, E. S. Kuh, and D. Wang, "Post global routing crosstalk risk estimation and reduction," in *Proceedings of the IEEE/ACM International Conference on Computer-Aided Design*, pp. 302–309, 1996.

- [14] H. Zhou and D. F. Wong, "Global routing with crosstalk constraints," in *Proceedings of the ACM/IEEE Design Automation Conference*, pp. 374– 377, 1998.

- [15] C. L. Phillips, Signals, systems and transforms, ch. 7. Upper Saddle River, N.J.: Prentice Hall, 2nd ed., 1999.

- [16] J. Rubinstein, P. Penfield, and M. A. Horowitz, "Signal delay in RC tree networks," *IEEE Transactions on Computer-Aided Design*, vol. CAD-2, no. 3, pp. 202– 211, 1983.