### Center for Spintronic Materials, Interfaces, and Novel Architectures

# **Exploiting Non-Volatility**in Spin-Based Information Processing

X. Sharon Hu, University of Notre Dame

Students: Robert Perricone, Ibrahim Ahmed Collaborators: Michael Niemier, Chris Kim, Anand Ragunathan, Sachin Sapatnekar Jian-Ping Wang

### Theme 5 Cross Theme 4

This work is sponsored in part by C-SPIN, a funded center of STARnet, a Semiconductor Research Corporation (SRC) program sponsored by MARCO and DARPA.

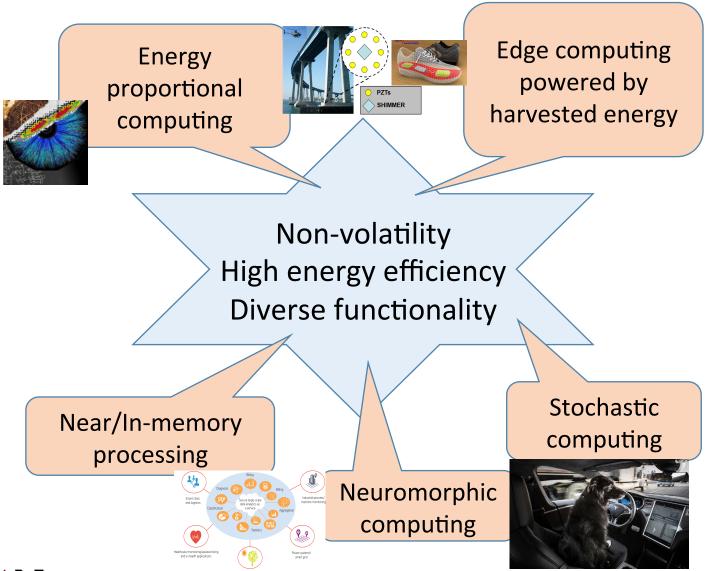

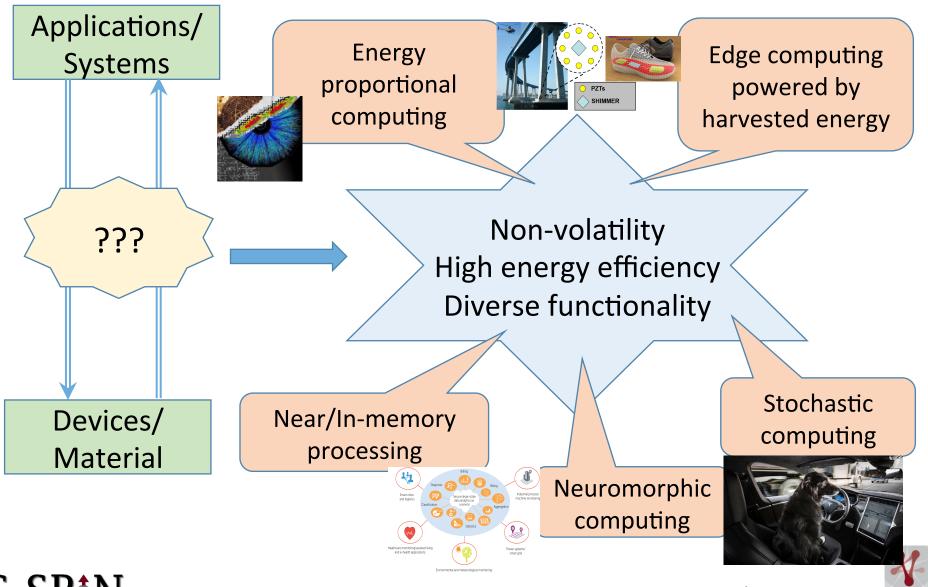

### From Applications to Devices

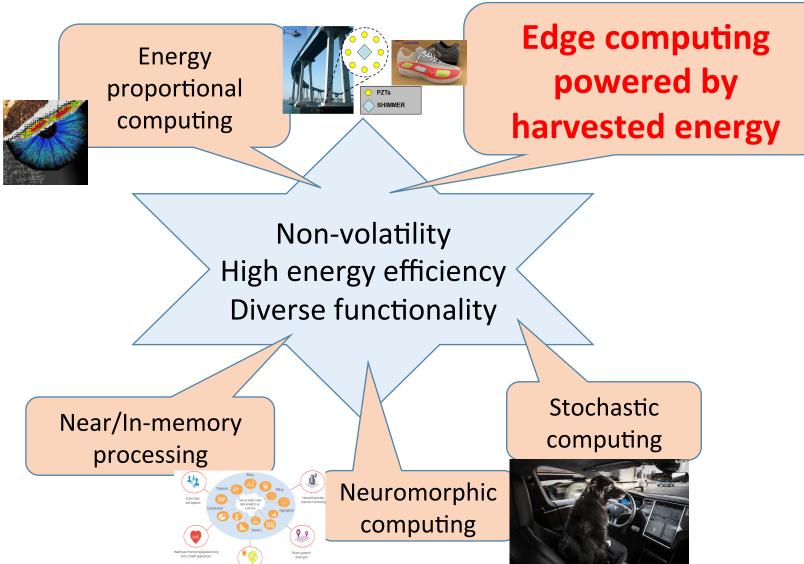

### **Exploiting Unique Properties of Spintronic Devices**

C-SPIN, Annual Review, September 20, 2016

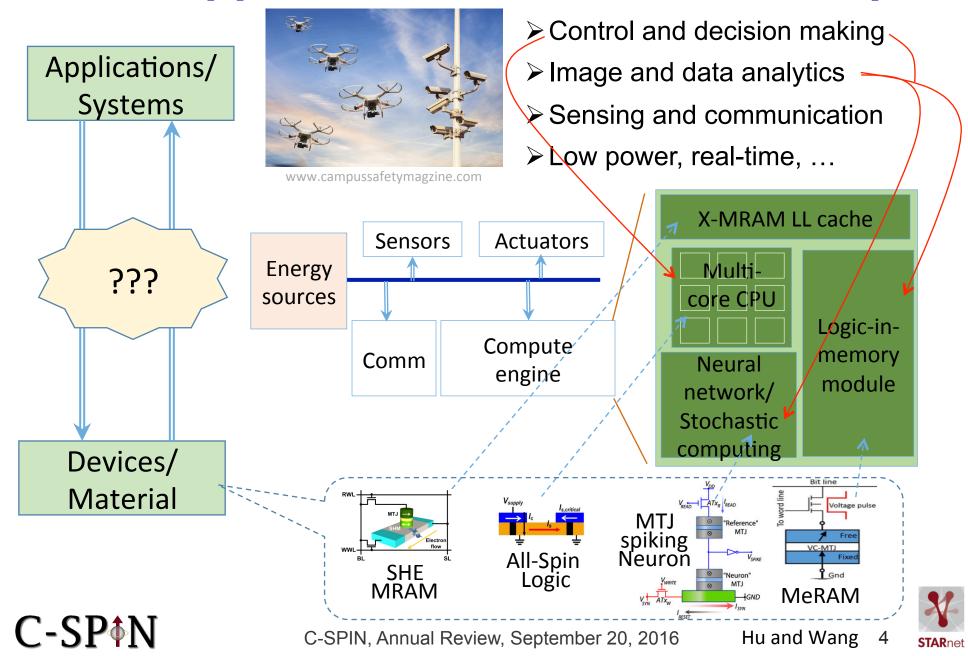

### From Applications to Devices: Example

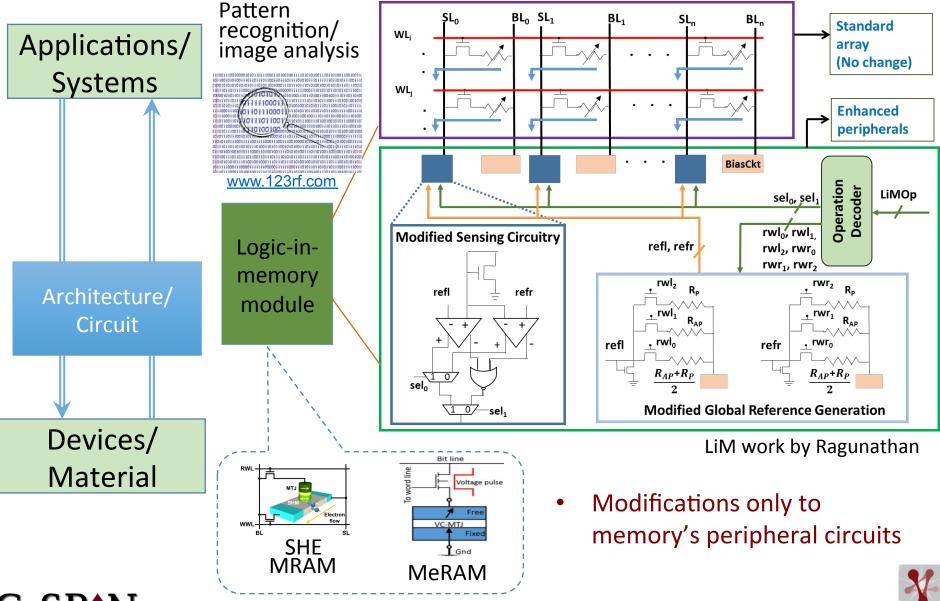

### Circuit and Architecture Example

# **Exploiting Unique Properties of Spintronic Devices**

### Systems Powered by Harvest Energy

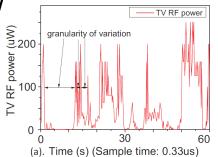

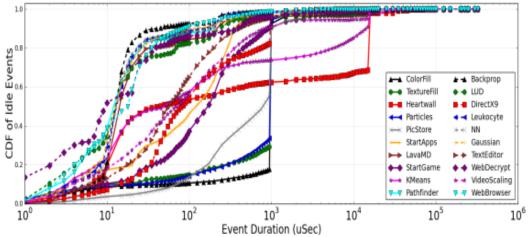

➤ Many edge computing systems are powered by harvested energy

- ➤ Unstable power supply

- Off time varies from cycle-to-cycle

- Length outage depends on source

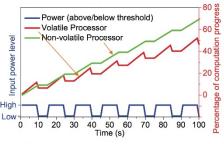

Frequent backup/ recovery

- Energy inefficiency

- Slow progress

- NV components allows faster progress toward end result

Fig. 4. VP vs. NVP processing progress comparison

#### Non-volatility of spintronic devices can be ideal alternatives

Power profile figure from: Ma, K., et al. "Architecture exploration for ambient energy harvesting nonvolatile processors." *IEEE Int'l Symposium on High Performance Computer Architecture (HPCA)*. IEEE, 2015.

### **Non-Volatile Processors (1)**

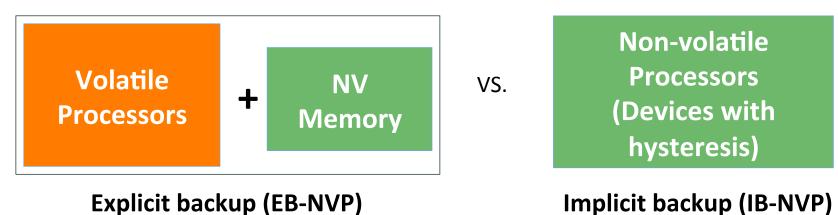

#### ➤ Two basic designs

#### **≻EB-NVP**

- NV memory for retaining data during power outage

- C-SPIN memory devices (SHE-RAM, AFM-RAM, ME-RAM)

- Write time/energy, read time/energy, retention time

#### **≻IB-NVP**

- NV logic devices themselves for retaining data during power outage

- C-SPIN computing devices (ASL, MESO, SWD, etc.)

- Processing energy, delay, retention time

### **Non-Volatile Processors (2)**

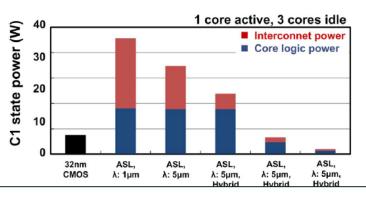

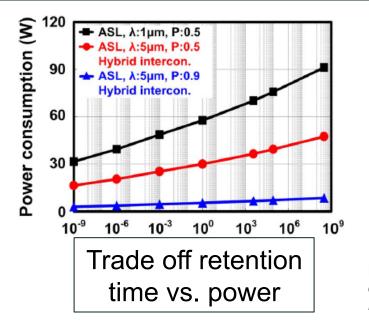

Energy may be less competitive for general purpose computing

#### NV processor with hybrid backup

NV Memory

Spin devices (s.t. ASL, MEL) are good candidates

+

- Shorter retention time for NV processor to save energy

- NV memory recovery only needed when outage is long

- Use design space exploration to optimize

Figures taken from: Kim, J, et al. "Spin-based computing: device concepts, current status, and a case study on a high-performance microprocessor." *Proceedings of IEEE,* 2015..

### Framework for Benchmarking Non-Volatile Processors

### Power supply profile modeling

- Total # of backups/Recovery

- Distribution of Power Outage

### Processor architecture modeling

- # of PE types

- # of PEs/PE type

- Interconnects

### Backup strategy modeling

- Energy/Delay per NV memory read and write

- # of Writes/Reads per backup/recovery operation

### NV processor modeling

Total processor energy/delay

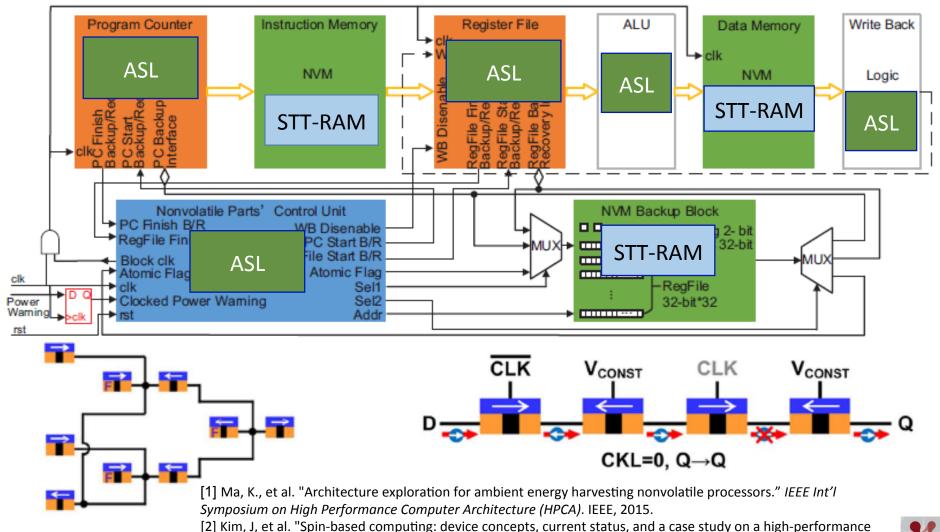

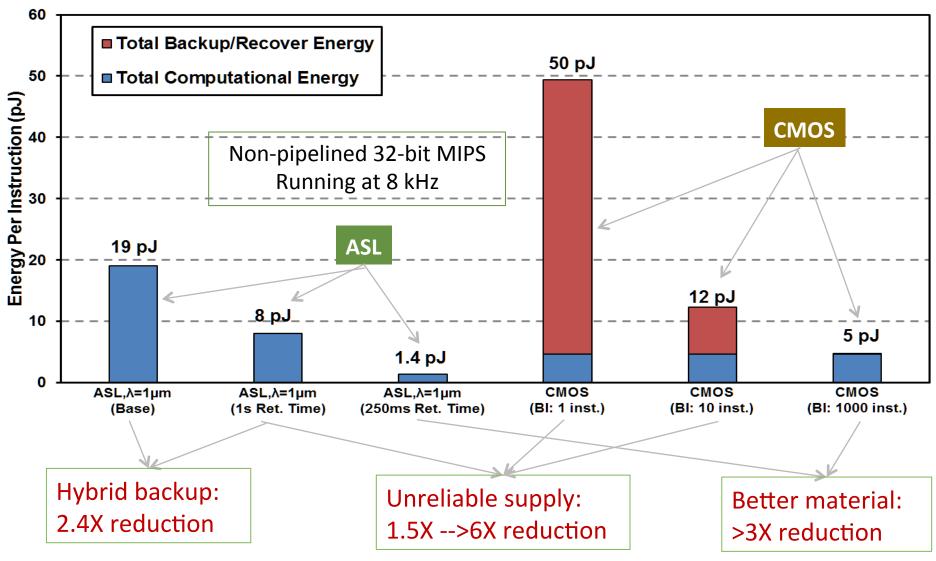

### Case Study: 32-Bit MIPS Processor

#### >32-bit non-pipelined MIPS processor [1]

microprocessor." Proceedings of IEEE, 2015.

C-SP

N

C-SPIN, Annual Review, September 20, 2016

### Case Study: ASL as Drop-In Replacement

### ➤ CMOS processor data derived from [1]

- Original data in [1] based on 45nm technology

- Used BCB model to scale down the processor to 15nm technology

- Both transistors and STT-RAM are scaled

### >ASL processor data derived from [2]

- Number of ASL devices (for RF, PC, ALU, Control, etc.): 3500 (50% of total number of transistors)

- IC Buffers: 0 (based on probability distribution function in [2])

- Different diffusion lengths and materials are considered

- $E_{total} = N_L(E_L) + N_{IC}(E_{IC})$

- N<sub>I</sub> and N<sub>IC</sub> are # of logic and IC buffers, resp.

- E<sub>L</sub> and E<sub>IC</sub> are the switching energy per device

[1] Ma, K., et al. "Architecture exploration for ambient energy harvesting nonvolatile processors." *IEEE Int'l Symposium on High Performance Computer Architecture (HPCA)*. IEEE, 2015.

[2] Kim, J, et al. "Spin-based computing: device concepts, current status, and a case study on a high-performance microprocessor." *Proceedings of IEEE*, 2015.

### Comparing ASL with CMOS NVP

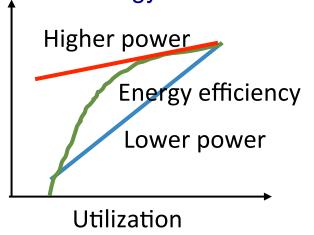

### **NV** in Energy Proportional Computing

- ➤ Idle power in heterogeneous multi-core systems

- Can be quite significant

- Application dependent

- ➤ Aim to achieve energy proportional computing

- ➤ Our preliminary results show an Intel i5 processor running BFS only spends about 30% of time, 50% energy in the active mode

M. Aroraet al., "Understanding idle behavior and power gating mechanisms in the context of modern benchmarks on CPU-GPU Integrated systems," HPCA, 2015, pp. 366-377.

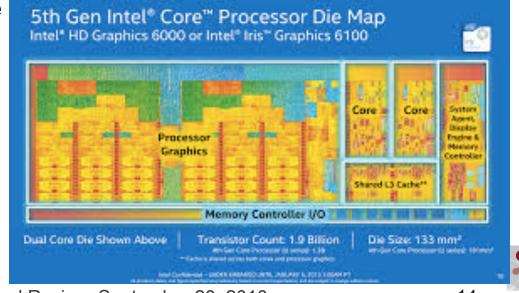

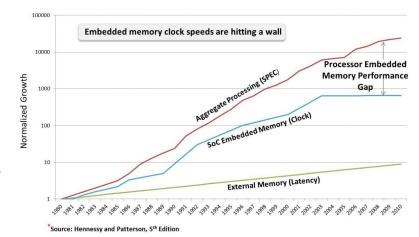

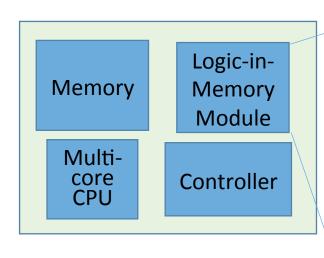

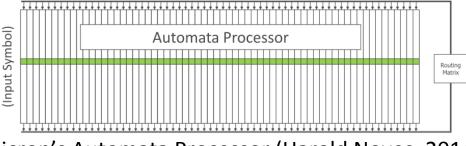

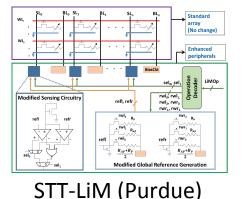

### **NV** in Near/In-Memory Processing

- ➤ Data analytics applications

- Large amount of data

- Simple operations

- ➤Place operations close to data

- Increase effective memory BW

- Reduce energy consumption

Micron's Automata Processor (Harold Noyes, 2014)

**Row Address**

BLB0 BL1 BLL **Computational RAM**

(Minnesota)

# **Exploiting Unique Properties of Spintronic Devices**